Verilog语法——2.模块例化、运算符

发布时间:2024-01-16 14:45:44

参考资料

【明德扬_verilog零基础入门语法HDL仿真快速掌握-手把手教你写FPGA/ASIC代码设计流程中的应用】

2 模块例化、运算符

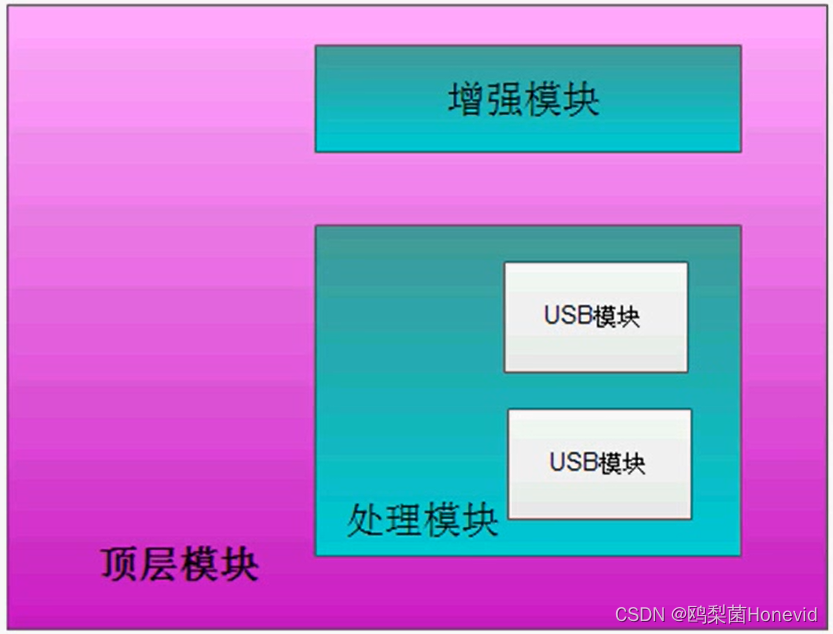

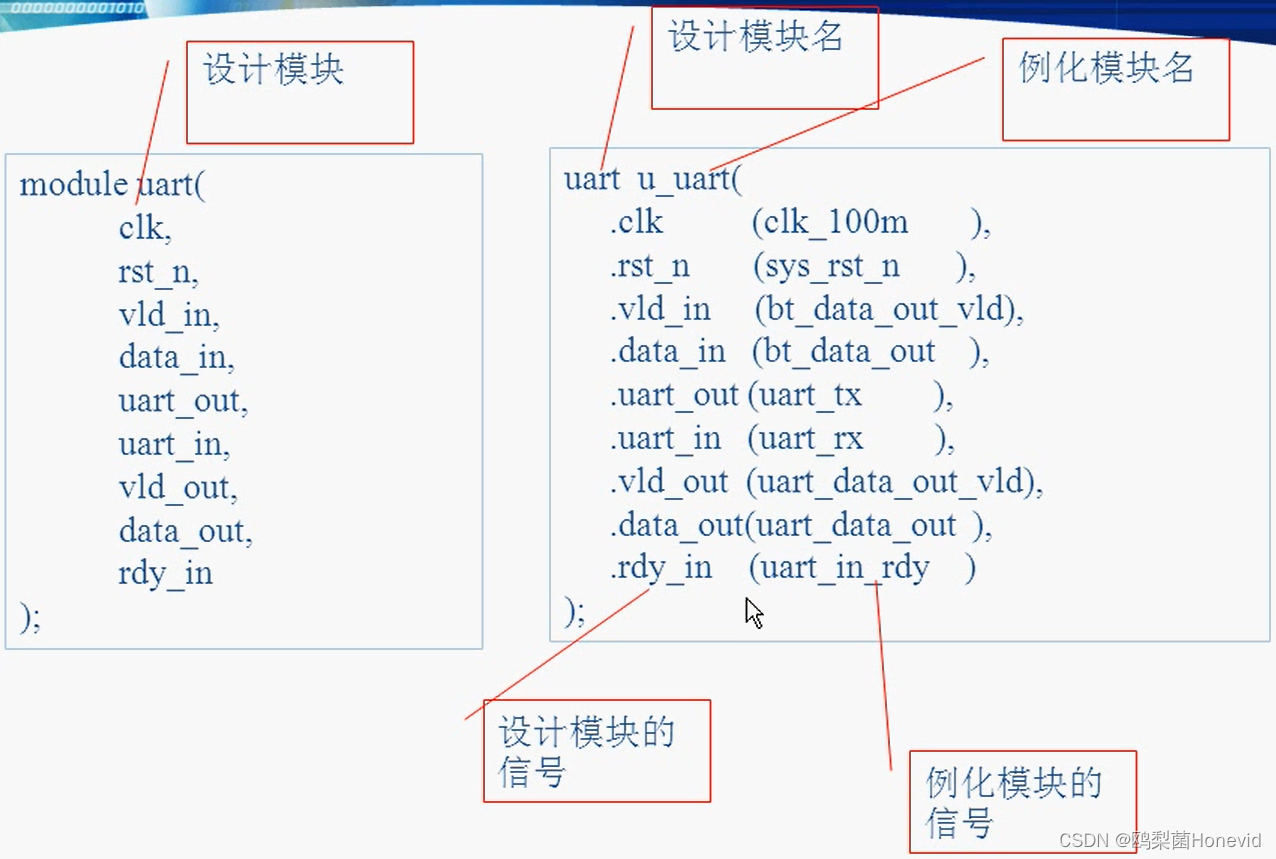

2.1 模块例化

2.1.1 什么是模块例化

例化,即将项目不断拆分成次级功能模块,然后从最简单的模块开始实现,进而完成整个复杂项目

2.1.2 模块例化的方法

针对已经抽象好的模块,需要进行语义化命名,以便后续的调试。

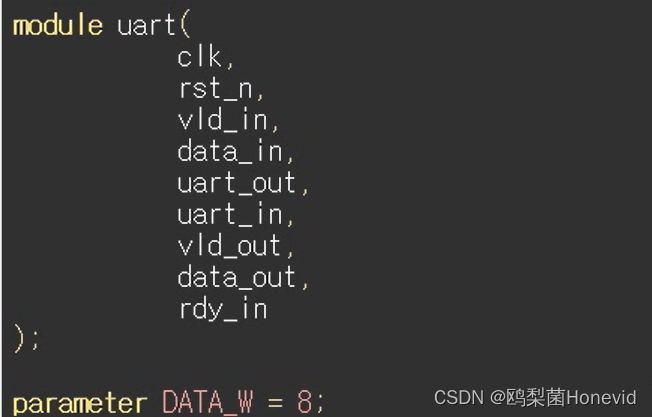

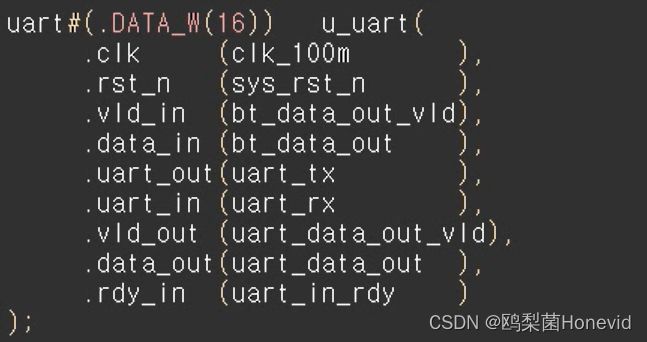

2.1.3 参数例化

在不改变原来模块大体内容的情况下,改变一个变量的位宽

参数例化的好处:在仿真测试时便于调整基准数据,例如仿真时钟时可以将基准时间从1秒改成0.001秒。

通过此方式,可以将原来模块中8位的DATA_W,在例化时改为16位

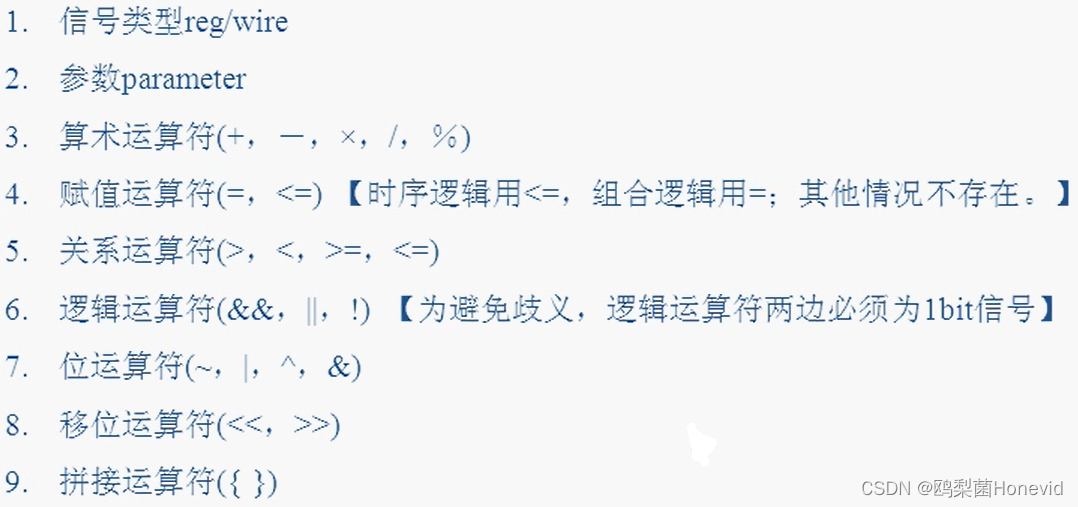

2.2 运算符

2.2.0 总览

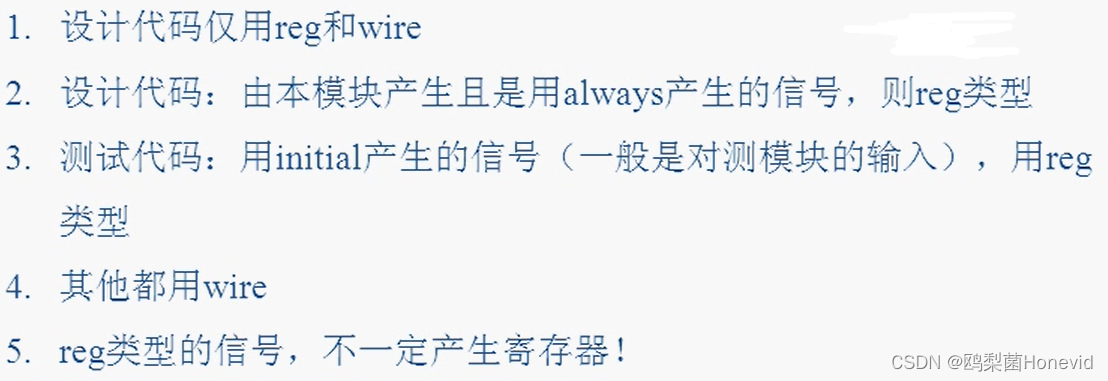

2.2.1 信号类型reg/wire

EXAMPLES

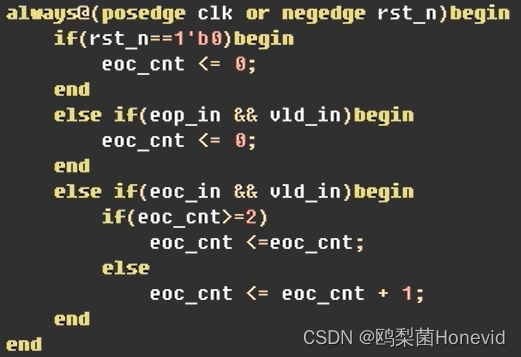

- 本模块always产生的信号,用reg eoc_cnt

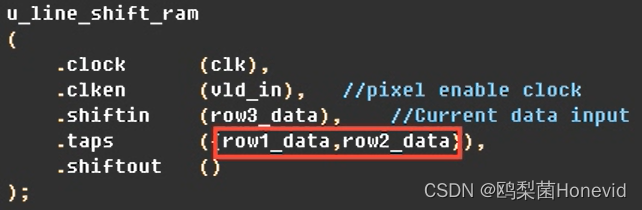

2. 本模块产生,非always,用wire row1,row2

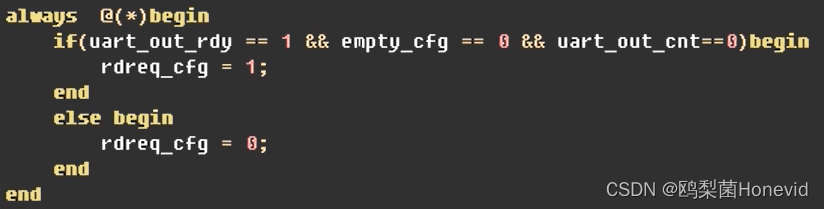

3. 本模块产生,是always,用reg rdreq

4. 肯定不是always产生的,使用wire sdata

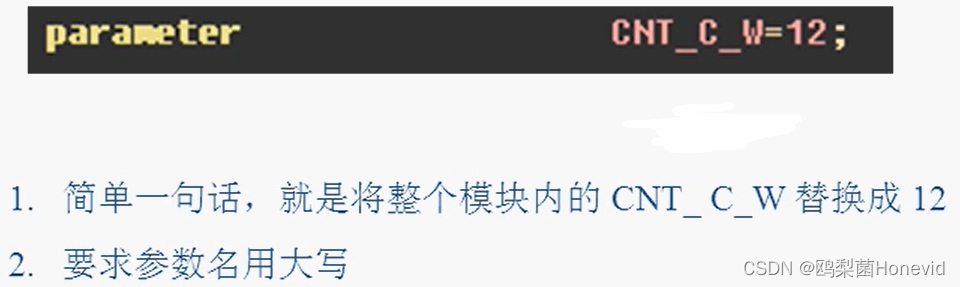

2.2.2 参数parameter(相当于c语言的宏定义)

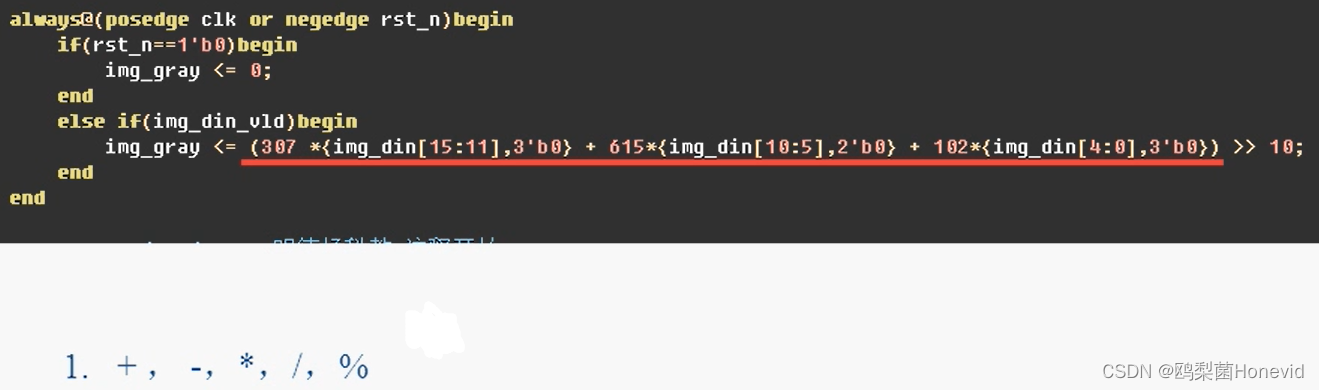

2.2.3 算术运算符

FPGA中,除法和求余需要大量的逻辑块,耗费资源多,因此需要尽量少用

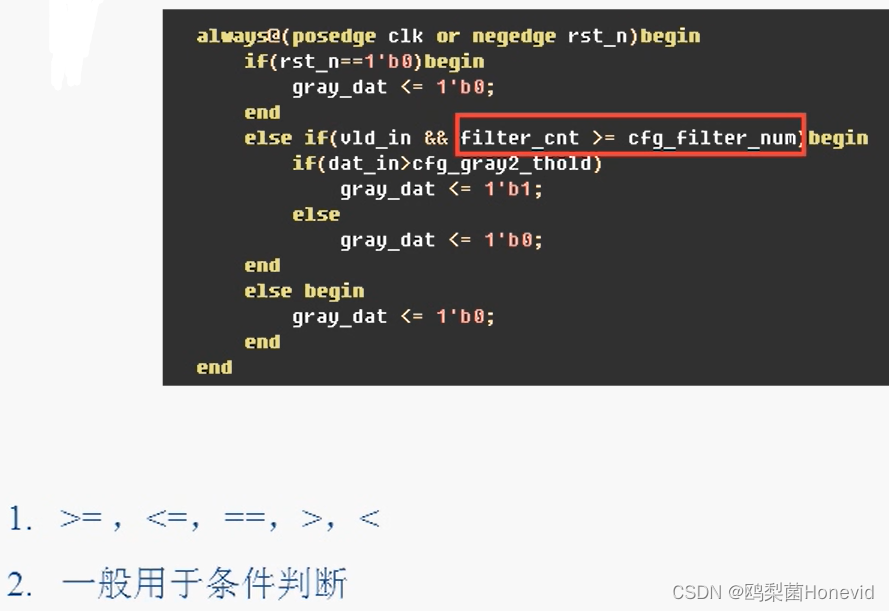

2.2.4 关系运算符

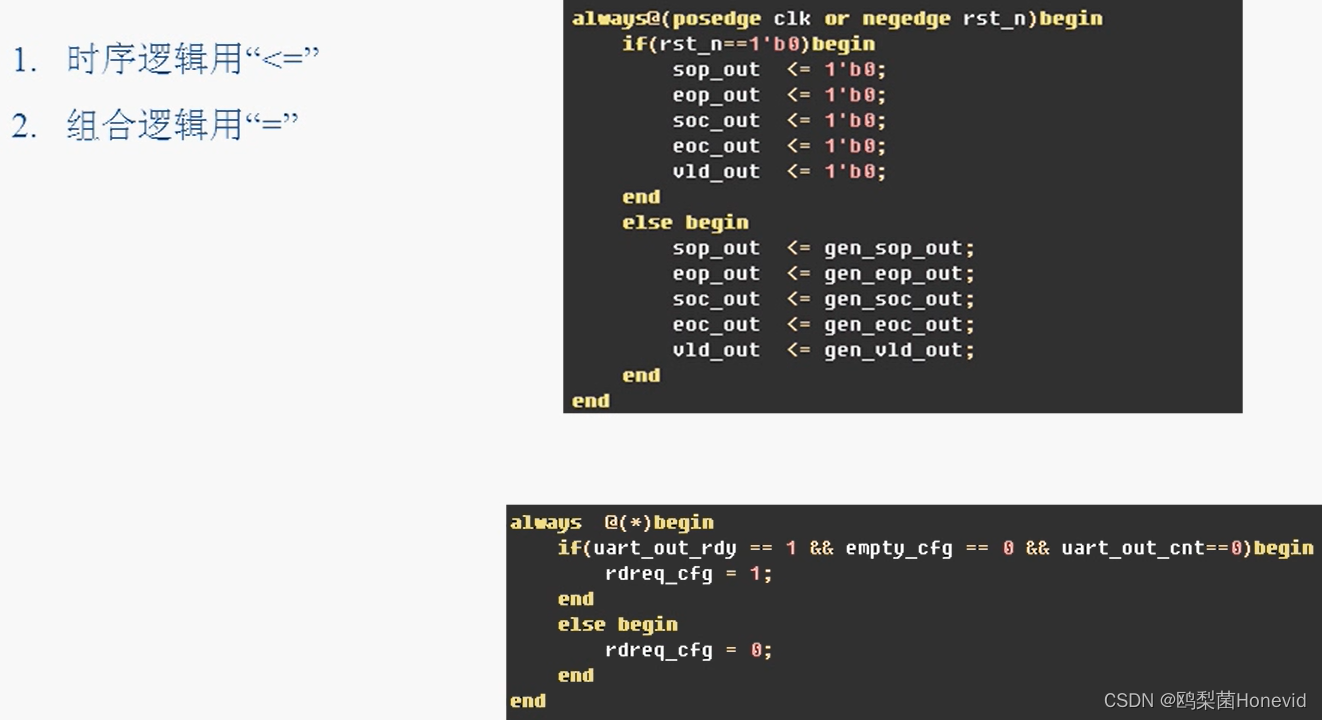

2.2.5 赋值运算符

不要搞复杂了

- 时序逻辑用: <=

- 组合逻辑用: =

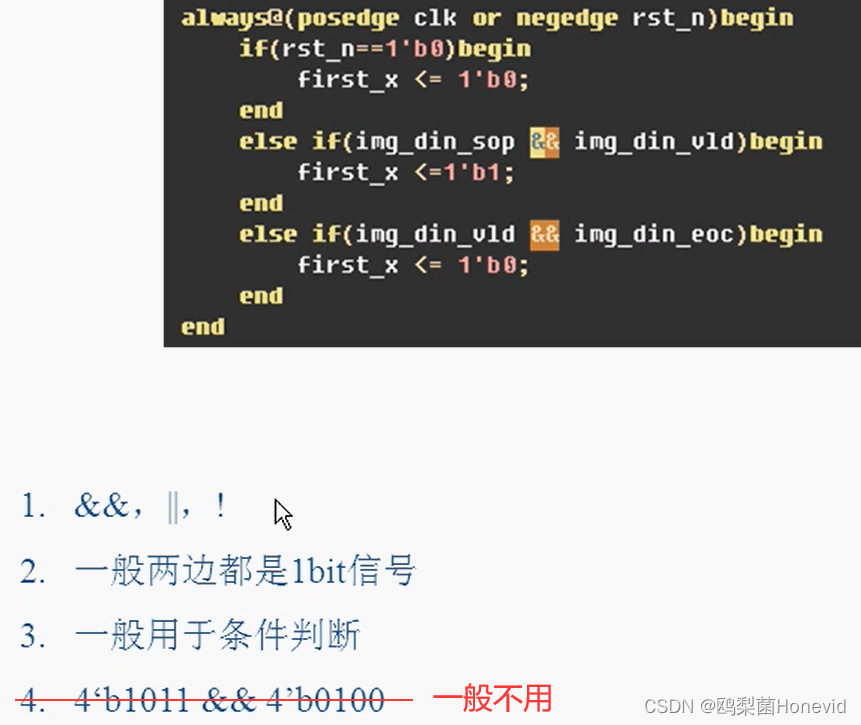

2.2.6 逻辑运算符

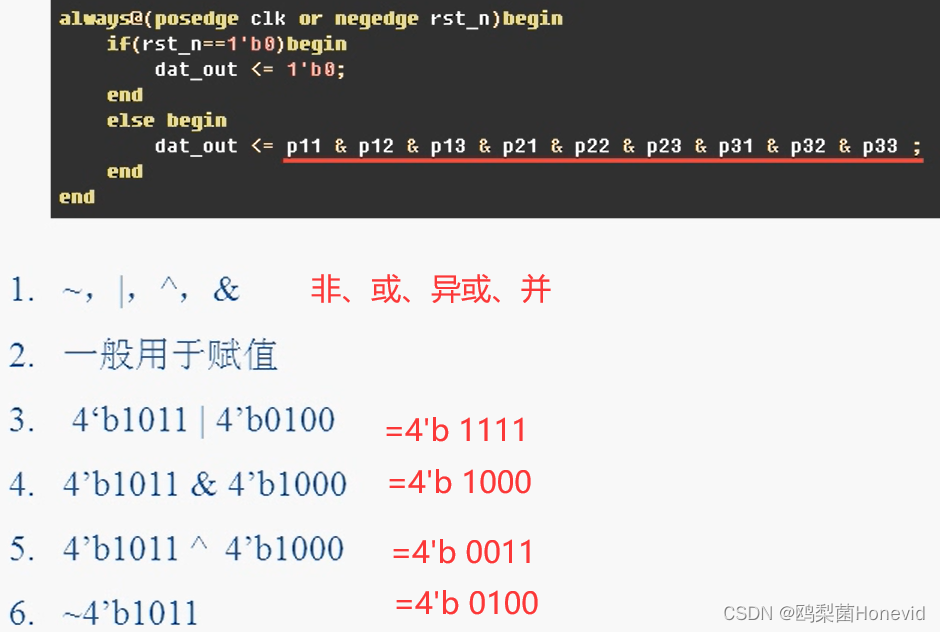

2.2.7 位运算符

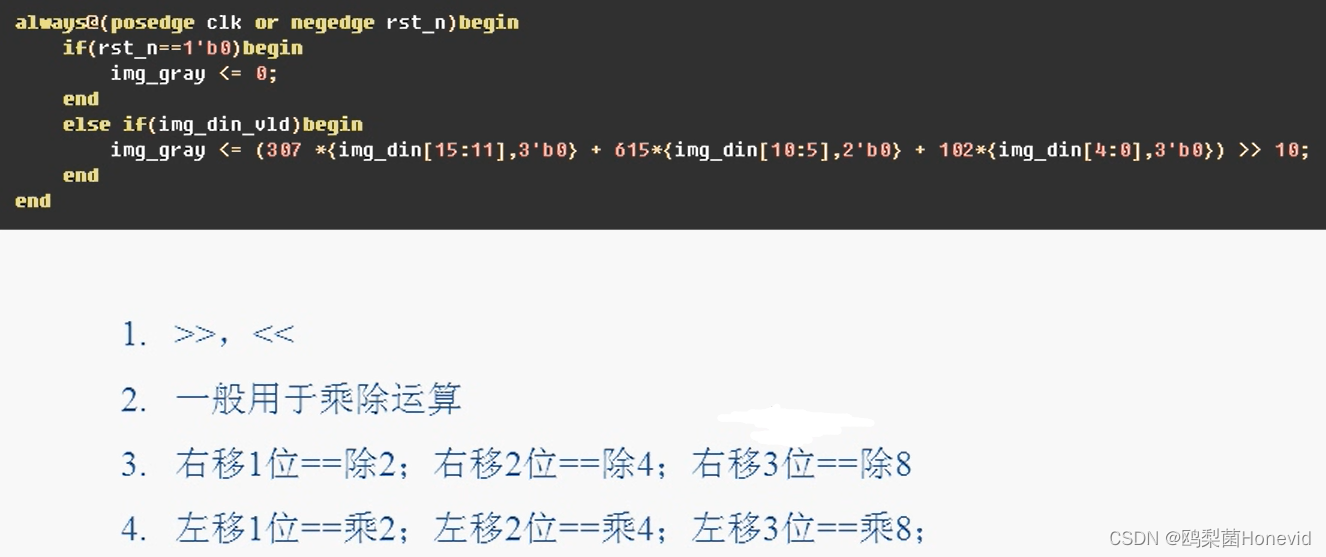

2.2.8 移位运算符

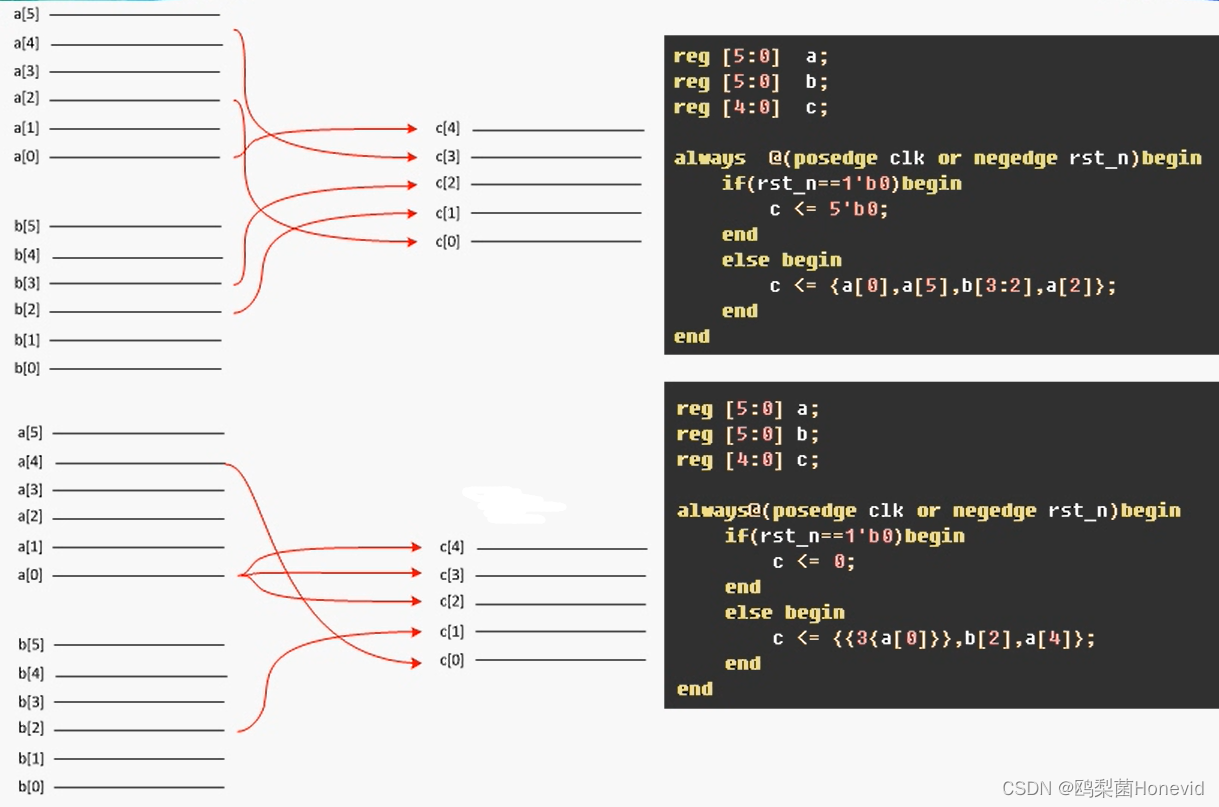

2.2.9 拼接运算符

多个相同的位数,可以用:{个数{a[n]}}实现重复拼接

文章来源:https://blog.csdn.net/qq_48035645/article/details/135485153

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。 如若内容造成侵权/违法违规/事实不符,请联系我的编程经验分享网邮箱:veading@qq.com进行投诉反馈,一经查实,立即删除!

最新文章

- Python教程

- 深入理解 MySQL 中的 HAVING 关键字和聚合函数

- Qt之QChar编码(1)

- MyBatis入门基础篇

- 用Python脚本实现FFmpeg批量转换

- 广泛关注!多家媒体集中报道 Mo 人工智能平台年终发布会

- JAVA开发工具Eclipse和MyEclipse

- 烟花代码C语言

- MySQL 8.0 架构 之错误日志文件(Error Log)(1)

- 喜报 | 联诚发斩获2023年度最佳舞美创意及租赁屏品牌

- 【机器学习】多模态机器学习

- 【计算机组成原理】期末复习试卷

- 用VSCode做Docker环境中的开发

- 婴儿专用洗衣机哪个牌子比较好?高性价比婴儿洗衣机推荐

- 亚马逊prime会员日活动是免费的吗?prime day怎么选产品促销?——站斧浏览器